With emerging, quantum-based logic gates and transistors, engineers will continue to shrink computer hardware and boost power and efficiency, even after traditional semiconductor technologies reach their scaling limits.

Traditional logic-gate devices are tiny switches, the building blocks of computer circuitry. Each receives two inputs and responds with an output of either “on” or “off.”

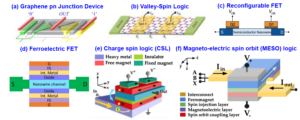

The new devices also act as traditional logic gates but are so novel that they will let circuits alternate between tasks. “Those new devices have new features, like reconfigurability, compared to traditional devices,” says Chenyun Pan, assistant professor of electrical engineering at the University of Texas at Arlington. “For example, some of the spintronic devices or multigate transistors have more terminals, allowing them to be reconfigured to different logic functionalities with a very compact area. We want to utilize those new features and put them into a circuit and system so we can improve the area and energy efficiency of the computation.”

To unleash the devices’ potential, researchers must develop a fast, scalable algorithm called a synthesizer. The synthesizer’s job is to automatically design reconfigurable circuits by matching new devices and their interconnections to the system in which they operate. The synthesizer will make discerning choices across all levels to optimize the circuits in terms of area (number of devices), delay (time to switch between functions and execute each) and energy use.

Pan is working to do just that. He has received a five-year Early Career Research Program Award from the Department of Energy Office of Science to develop such an automated cross-layer design framework, with the aid of a high-performance computing facility through a University of Texas STARs instrumentation grant.

In the traditional logic gate, “on” is represented as 1, “off” as 0. Differently designed logic gates perform various logical functions. An AND gate, for example, has an output of 1 only if both of its inputs are also 1. An OR gate responds with 1 when either or both of its inputs are 1. Logic gates of all types are combined to build computer circuits that carry out a range of tasks, from arithmetic operations to simulations of weather patterns and other complex phenomena.

These advances would trim the number of logic gates, reducing the size and power demand for every type of computing device.

The emerging technologies offer two game-changing traits. First, because the devices work via quantum properties such as electron spin and quantum tunneling, they are much smaller and more energy efficient than traditional technologies, which are labeled complementary metal-oxide-semiconductor (CMOS) devices. Second, many logic gates based on novel post-CMOS technology can stand in for two or more traditional gates. In fact, these logic gates can swap roles instantly during runtime, working first as an AND gate, for example, then changing hats to perform as another gate type and back again.

These advances would trim the number of logic gates, reducing the size and power demand for every type of computing device. For high-performance computing, they could advance the effort to achieve exascale, machines that can execute 1 million trillion operations per second. Laptops and smartphones would also be lighter and less power-hungry.

“And some devices don’t even have a battery,” Pan says, referring to ultra-low-power hardware that depends on solar or piezoelectric energy. “They don’t have a very reliable power supply, and they can also take advantage of these compact and low-power reconfigurable circuits.”

To streamline circuit reconfiguration, Pan is adapting the traditional idea of synthesizers that optimize the arrangement and interconnections of devices within a circuit to satisfy logical, or Boolean, requirements. These algorithms are termed “SAT-based,” for their ability to satisfy Boolean requirements. The modification includes an encoding method that will find and optimize circuits that satisfy multiple functionalities and can be controlled by a circuit’s terminal. “The most challenging part is to develop an algorithm that can do a large-scale circuit synthesis, because a practical circuit and system would consist of millions of logic gates.”

His algorithm begins by searching for standalone circuits that share much of the same configuration, in which each satisfies the Boolean requirements of the desired reconfigurable circuit. To find such matching circuits among millions of nodes, the synthesizer uses a novel filter that reduces the search space by first examining only the circuits’ topology – their node amounts, their arrangement and the connections among them. Because many gate types can perform different operations, the algorithm ignores that factor at first.

Once two matching circuits emerge, the synthesizer searches within them to ensure that the device type at each node can alternate between the roles it must play. The synthesizer partitions the matching circuits into blocks that correspond to one another, optimizes a new configuration in each block and, finally, re-integrates the blocks into one reconfigurable circuit.

Matching circuits will share many, but not all, surface features. That means each reconfigurable circuit also will include additional nodes that operate during just one of the functions. Pan’s synthesizer systematically optimizes placement of these additional nodes. An SAT-based algorithm will solve shared circuit elements to let the system toggle between the two main functions, with each node changing its logic operation on the fly as needed.

With his collaborator, Shaloo Rakheja at the University of Illinois Urbana-Champaign, Pan also is working to model the building blocks of reconfigurable circuits – the devices themselves – while various groups around the globe actively develop them. The co-workers will evaluate several of the many devices to determine which are the most promising. Rakheja is an expert in modeling such reconfigurable emerging devices, and their work in some cases could use novel materials.

The models will be assembled in a library of virtual devices, or reconfigurable logic cells, for use in simulations. Pan and Rakheja will be able to provide feedback to experimenters and device developers regarding how the hardware performs in the cross-layer synthesis of a complete reconfigurable system. “We will perform a comprehensive benchmarking for a variety of emerging reconfigurable devices and quantify their potential benefits against their CMOS counterparts,” Pan says.

Pan and his colleague Liuting Shang at UT-Arlington ran a simulation of reconfigurable circuits that an early version of the synthesizer designed. In a paper under preparation for publication, they report results on a system built using a reconfigurable logic device called a spin-valley logic gate, co-designed with Azad Naeemi, who was Pan’s Georgia Institute of Technology Ph.D. advisor. Compared to an equivalent CMOS system, the reconfigurable circuits showed a 38% reduction in the number of gates needed and a 78% reduction in a combined measure of the system’s size, energy consumption and speed.

“The promising preliminary result is for a relatively small-scale circuit,” Pan says. “A real circuit, a real system, will have thousands or even millions of logic gates, so we need to improve the scalability of these algorithms so that they can be applied for very large-scale circuits.”